Az Intel már a 65 nanométeres csíkszélességű gyártástechnológiát teszteli

Az Intel hillsboroi (Oregon, USA) D1D félvezetőgyártó üzemében 65 nanométeres csíkszélességű technológia felhasználásával működőképes SRAM chipeket gyártott -- jelentette be Mark Bohr, az Intel gyártástechnológiai fejlesztésekért felelős vezetője. A vállalat állítása szerint a 65 nanométeres csíkszélességű alkatrészek sorozatgyártása a korábbi terveknek megfelelően 2005-ben kezdődik meg.

Az új, P1264 kódnevű, 65 nanométeres félvezetőgyártási technológia többek között magában foglal a korábbinál nagyobb teljesítményű és alacsonyabb fogyasztású tranzisztorokat, második generációs "feszített szilíciumot", nagy sebességű rézalapú átkötéseket és kis k-együtthatójú dielektrikummal történő szigetelési technológiát. A P1264 nyolcrétegű félvezető alkatrészek előállítását teszi lehetővé 300 milliméter átmérőjű szilíciumszeleteken.

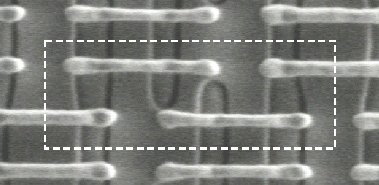

Az Intel által a D1D üzemben legyártott 4 Mbit kapacitású SRAM memóriachipek cellánként mindössze 0,57 µm2 méretűek, egy SRAM cella összesen hat tranzisztort tartalmaz. A 65 nanométeres csíkszélességű gyártástechnológiával 1 mm2 területen 10 millió tranzisztor helyezhető el -- ez a terület hozzávetőleg azonos egy golyóstoll hegyével.

65 nanométeres csíkszélességgel gyártott SRAM cella

A P1264 technológiával gyártott tranzisztorok kapuhossza mindössze 35 nanométer. Az Intel állítása szerint 2005-ben ezek lesznek a legkisebb és legnagyobb teljesítményű tranzisztorok, amelyeket sorozatgyártásban alkalmaznak. A jelenlegi tömegtermelésben alkalmazott legfejlettebb, 90 nanométeres Intel-technológia segítségével 50 nanométeres kapuhossz érhető el. A 130 nanométeres csíkszélességű Pentium 4 "Northwood" processzort felépítő tranzisztorok kapuhossza 60 nanométer.

A 65 nanométeres csíkszélességű gyártástechnológia fejlesztéséhez és első implementálásához használt D1D chipgyár az Intel legfejlettebb üzeme, egyben a legnagyobb tisztaszobával rendelkezik. A D1D gyárban a tisztaszoba mérete 20 ezer négyzetméter. Az Intel termelési környezetben használt gyárai közül egyedül a mexikói Fab11X rendelkezik nagyobb tisztaszoba-területtel, azonban ez a gyár két épületből áll és két tisztaszobát tartalmaz. A hillsboroi D1D üzem 300 milliméter átmérőjű wafereket dolgoz fel, ezek szállítása teljesen automatizált. A gyár a 65 nanométeres technológia fejlesztése mellett a 45 nanométeres technológia fejlesztésének helyszíne is.

Az Intel D1D félvezetőgyára

Bohr közölte, hogy a 65 nanométeres csíkszélességű alkatrészek gyártásához az Intel számos már meglevő, 193 nanométeres hullámhosszúságű litográfiai berendezést fel tud használni, ami jelentősen csökkenti a gyártási költségeket. A sikeres fejlesztésben oroszlánrésze volt az Intel fotómaszkokat fejlesztő részlegének, az ún. fáziseltolásos technológia teszi lehetővé, hogy a 193 nanométeres litográfiai berendezésekkel akár 40 nanométeres struktúrák is létrehozhatóak legyenek. Az Intel várhatóan a 45 nanométeres csíkszélességű alkatrészek fotómaszkjait is részben vagy egészben 193 nanométeres litográfiai berendezésekkel tervezi előállítani.