Sínen van a DDR5 és NVDIMM-P szabványosítása

Nyáron érkezhet a szabványtervezet, de a piaci rajthoz még legalább két év kellhet.

Jól haladnak a DDR5 és az NVDIMM-P szabványok lefektetésének munkálatai - adta hírül a különféle memóriák szabványosításával foglalkozó JEDEC iparági szervezet. A DDR5 (ami nem keverendő a GDDR5-tel) szabványtervezetét már júniusban prezentálná a testület, amennyiben pedig minden a terv szerint halad, úgy jövőre elkészülhet a végleges specifikáció. Ezután jellemzően egy év kell az első, piacképes termékek megjelenéséhez, szélesebb körű terjedésre viszont 2020 előtt nem számíthatunk.

Bár egyelőre a tervezet részletei sem ismertek, a gyártók elképzelései szerint a DDR5 az elődök által kitaposott úton megy majd tovább, forradalom helyett inkább az evolúciót preferálva. A konzervatív megközelítés egyik oka a költségek szinten tartásában rejlik, a forradalmi újítások ugyanis rendszerint komolyabb befektetéseket igényelnek, a fejlesztési és implementációs kiadások mellett pedig a termékek gyártása is hosszú ideig jelentősen drágább. A fejlesztéshez a DDR4-nél végül elnapolt, de azóta a GDDR5X-szel piacra dobott módszert képzeli el a szabvány továbbfejlesztéséhez a Micron, 16-ra emelve a memóriasínre küldött adatszavak számát.

A DDR4 esetében ezt elsősorban két okból halasztották el: a memórialapkák területe jelentősen megnőtt volna az extra kivezetések miatt, illetve a 16 szavas beolvasás nem passzolt volna a processzorok 64 bájtos cache vonalmérethez. Emiatt az aktuális szabványban két bankcsoportot hoztak létre, így a DDR4 kétszer nyolc memóriabankot tartalmaz, egy-egy csoportba szedve úgy, hogy egyetlen chipben négy darab négy bankból álló csoport található, melyekből a vezérlés egyszerre kettőt vagy négyet választhat ki. A DDR5 ezt is növelné, a 16 szavas beolvasás mellett 16-32 bankot képzel el összesen nyolc csoportban a Micron, az emiatt növekvő lapkaterületet pedig a legmodernebb, már 20 nanométer alatti csíkszélességgel kompenzálná a gyártó.

A hazai IT felrázásához haza kell hozni a legjobbjainkat Az elvándorolt szakemberek visszacsábítása komoly kihívás, azonban számos ország már megmutatta, hogy ez nem lehetetlen feladat.

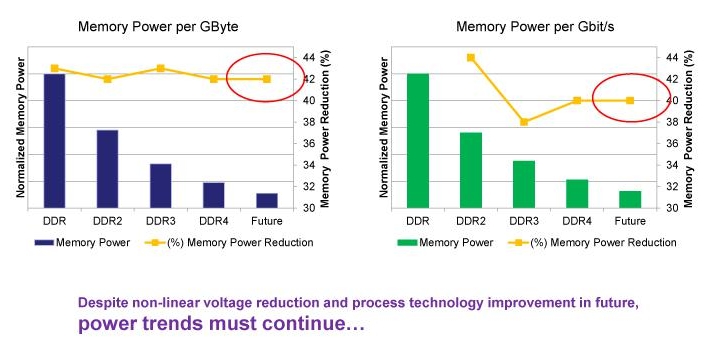

A fejlesztésekkel a DDR5 megduplázná az egységnyi magórajellel elérhető sávszélességet, így a szabvány effektív 3200-tól 6400 MHz-ig skálázódna. Emellett a feszültség is csökkenne, a DDR4 1,2 voltos értéke 1,1 voltra mérséklődne, minek köszönhetően csökkenne a fogyasztás, összességében pedig az elődhöz hasonló sávszélességet lényegesen kisebb disszipáció mellett lehetne elérni. A chipek kapacitása is gyarapodna, a már említett Micron például 8-32 gigabittel számol, tehát a legnagyobb komponens 4 gigabájtos lenne.

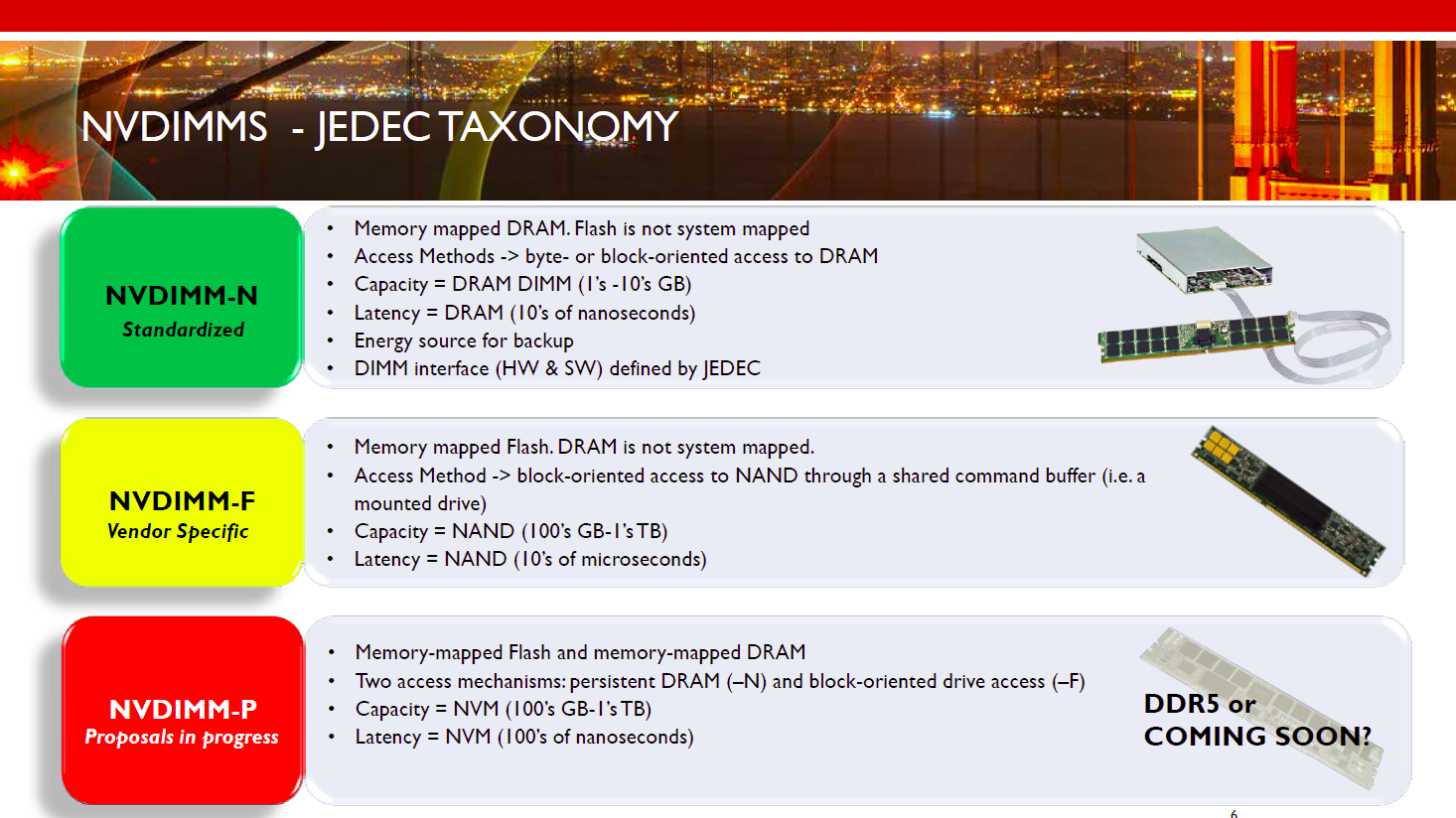

Jöhet a szabványos NVDIMM-P

A DDR5-tel párhuzamosan érkezhet a részben arra épülő NVDIMM-P. Ilyen modulokat többek között már a HPE és a Netlist is kínál, ugyanakkor ezek nem szabványos megoldások, a gyártók jóformán kényük-kedvük szerint alakíthatják ki a termékeket a kompatibilitás tetszőleges szem előtt tartása mellett. A JEDEC erőfeszítésének hála ez is változhat, a testület az NVDIMM-N után az NVDIMM-P-t is szabványosítja. Míg előbbi egy tisztán DRAM chipekre épülő, a háttértárakhoz képest relatíve kis kapacitású, az adatbiztonság növeléséhez külső (akkumulátoros) tápellátással megtámogatott modul, addig az NVDIMM-P egy DRAM+NAND hibrid, ahol az áramkimaradás elleni védelemről a nem felejtő (vagy nem volatilis) chipek gondoskodnak, melyek nem utolsó sorban lényegesen nagyobb bitsűrűségüknek hála a modul kapacitását is jelentősen növelhetik.

Ezzel optimális esetben SSD-szerű kapacitás, üzembiztos működést, illetve DRAM közeli sebességet rakható össze, ugyanakkor ehhez a modulra egy megfelelő vezérlőchip is szükséges, ami a DRAM és a NAND-ok, azaz a két eltérő típusú memória közti folyamatos adatrendezést biztosítja. Amennyiben a kért adat a lassabb NAND chipeken van, úgy azt a vezérlés még az lekérés előtt igyekszik átmásolni a gyorsabb DRAM-ba, ezzel biztosítva a DRAM-közeli olvasási sebességet és késleltetést. Bár a JEDEC elképzelése egyelőre nem ismert, az ilyen modulokra (tantál) kondenzátorok egy csoportja is felkerül, az áramellátás megszűnésekor az ezekben eltárolt energia biztosítja a vezérlés ideiglenes tápellátását, amely így képes a DRAM chipekben ragadt adatot átmenteni a tartalmát áramellátás nélkül is megőrző NAND-ba.

Az ilyen modulok szinte teljes egészében az adatközpontokba kerülnek, ahol az NVDIMM-mel kialakítható memóriahierarchiával jelentősen gyorsítható a rendszer válaszideje. Ehhez ugyanakkor a szoftveres oldalt át kell alakítani, hisz a programok bátrabban nyúlhatnak a memóriához, már a folyamatos, gyors elérést igénylő, de kritikus fontosságú adatok is tárolhatóak a modulokban, miközben a gyorsabb elérésből nem, vagy csak kevésbé profitáló adatok maradhatnak alsóbb szinteken, a háttérárakon.