3D tranzisztorokat gyárt az Intel

A HWSW korábbi sejtései beigazolódtak: az Intel ma hivatalosan is bejelentette, hogy az idén tömegtermelésbe álló 22 nanométeres csíkszélességű gyártástechnológiájában a világ elsőként alkalmaz háromdimenziós tranzisztorokat.

A CMOS tranzisztor meghódítja a harmadik dimenziót

Az Intel először 2002-ben beszélt a háromkapus tranzisztorral kapcsolatos fejlesztéseiről, vagyis a cégnek közel egy évtizedébe telt, hogy az elméletet átültesse a gyakorlatba. 2003-ban még úgy tűnt, a vállalat akár 2007-ben, a 45 nanométeres eljáráson is bevetheti az elgondolást, azonban erre még a 32 nanométeres csíkszélességen sem került sor - hogy technológiai akadályokba ütközött a fejlesztés vagy üzleti okok állnak a háttérben, nem tudni. Az új tranzisztorok végül a P1270 kódnevű 22 nanométeres csíkszélességű eljáráson mutatkoznak be, amellyel a második félév során megkezdődik az Ivy Bridge processzorok tömeggyártása.

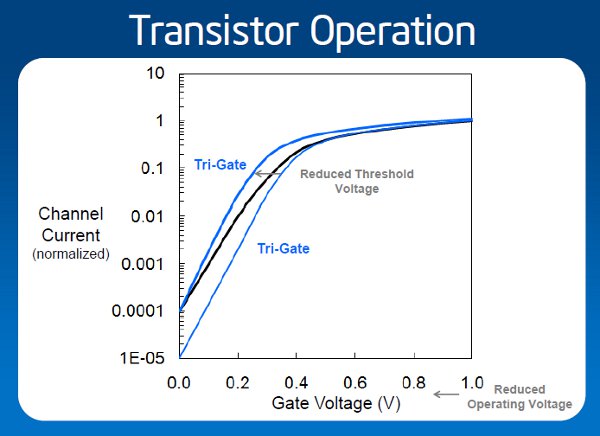

A háromkapus tranzisztorral a vállalat célja szokás szerint a teljesítmény növelése a fogyasztás csökkentése mellett, elsősorban a szivárgás letörése révén. A szivárgás a félvezetők lezárt átmenetén létrejövő jelenség, amely szabad elektronok és lyukak kombinációjából származik és nanoamper nagyságrendű. A szivárgási áram a tápfeszültséggel fordítottan arányos és egy kisebb csíkszélességű gyártástechnológia bevezetésénél többszörösére is nőhet, a jelenség megnyugtató kezelése ezért a gyártók egyik legfontosabb feladata - egy komplex, több milliárd tranzisztort tartalmazó chipben a teljes fogyasztás 30-40 százalékát is kiteheti. A jelenség féken tartható az áramkör "okos" tervezésével, órajel- és feszültségkapuzással, de a tranzisztorok szintjén is kezelni kell.

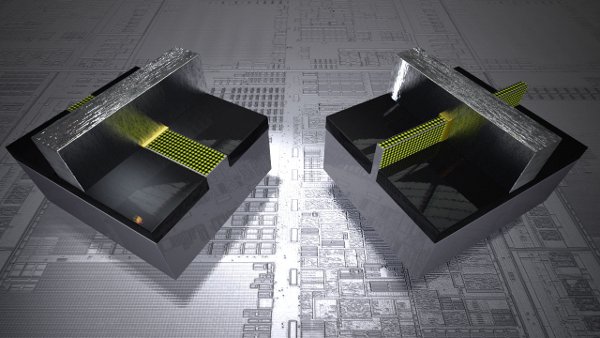

Az Intel által kifejlesztett és most tömegtermelésbe is vont háromkapus tranzisztor alkotóelemei nem rétegszerűen helyezkednek el mint ahogy az jelenleg megszokott, hanem háromdimenziós struktúrát alkotnak. A forrás (source) és a nyelő (drain) a szubsztrátból kiemelkedő vezetéken kap helyet, amelyet azonban három oldalán érintve (tri-gate) satuszerűen fog közre a kapuelektróda (gate), ami így "jobban zár" és segít csökkenteni a szivárgást.

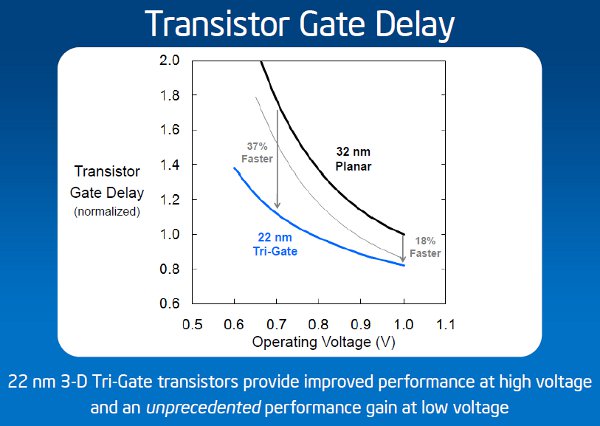

A háromkapus felépítés lehetővé teszi, hogy a lehető legtöbb áram folyjon át a csatornán amikor a tranzisztor bekapcsolt állapotban van, és a legkevesebb, amikor ki van kapcsolva, illetve hogy a leggyorsabb legyen az átmenet a ki- és bekapcsolt állapotok között. Az Intel által nyilvánosságra hozott adatok szerint a 22 nanométeres háromkapus tranzisztorok azonos fogyasztás mellett 37 százalékkal nagyobb kapcsolási sebességet tudnak elérni mint a 32 nanométeres planáris tranzisztorok, azonos teljesítmény esetén pedig mindössze fele annyit fogyasztanak.

"Az Intel tudósai és mérnökei gyakorlatilag újra feltalálták a tranzisztort, ezúttal a harmadik dimenzióba lépve" - méltatta a fejlesztést Paul Otellini, az Intel elnök-vezérigazgatója. A térbeli felépítés további előnye, hogy a tranzisztorok kisebb alapterületűek mint planáris társaik, sűrűbben helyezhetők el egy szilíciumszeleten, vagyis az alkatrészek miniatürizálása folytatódhat - a tájékoztatón elhangzott, hogy a 22 nanométeres eljáráson a 3D felépítésnek is köszönhetően kétszeres lesz a tranzisztorsűrűség a 32 nanométeres eljáráshoz képest.

"A 3D háromkapus tranzisztorral elérhető teljesítménynövekedés és fogyasztáscsökkenés semmihez nem fogható amit eddig láttunk" - mondta a bejelentés kapcsán Mark Bohr, aki a gyártástechnológiai fejlesztéseket irányítja az Intelnél. "Az előnyök jóval túlmutatnak azon, amit egy szokásos gyártástechnológiai váltásnál tapasztalunk. [...] Meggyőződésünk, hogy ezzel az Intel növelheti előnyét a többi chipgyártóval szemben." A 22 nanométeres eljáráson az Intel továbbra is alkalmazza a 45 és 32 nanométeres technológián bevezetett fejlesztéseket mint a germánium kapuoxid és a magas K együtthatójú dielektrikum.

Balra a planáris, jobbra a 3D tranzisztor

Vitatott technológia

Az Intel mellett korábban más félvezetőgyártók is beszéltek már háromdimenziós, többkapus tranzisztorokról, például az AMD, az Infineon és az IBM, de eddig egyetlen cég sem alkalmazott ilyen sorozatgyártásban. "Az igazán nagy kihívás ezt tömeggyártásba vinni" - mondta Mark Bohr, hozzátéve, hogy az Intel a 14 nanométeres eljárásával is kompatibilis az új tranzisztor, vagyis a 2014-re várható következő generációs technológián is minden bizonnyal ezeket használják majd. "A 14 nanométernél kisebb csíkszélesség eléréséhez azonban még további kutatás-fejlesztés szükséges" - mondta Bohr.

A 3D tranzisztorok megítélése egyébként egyelőre vegyes az iparban - a tavaly decemberi Applied Materials Future Transistor Forumon a Globalfoundries egyik műszaki vezetője, Witek Maszara egyértelműen a 3D tranzisztorok mellett tört pálcát, azt állítva, hogy ez a megközelítés biztosítja a legjobb teljesítmény-fogyasztás karakterisztikát. Az IBM részéről Ghavam Shahidi úgy vélekedett, a 3D tranzisztorok "ígéretesek", azonban nehéz őket tömegtermelésben alkalmazni és előbb-utóbb ezek is szivárgási gondokkal fognak küzdeni, ami hosszú távon megkérdőjelezi a létjogosultságukat.

Thomas Skotnicki, az STMicroelectonics "Advanced Devices" részlegének vezetője azon véleményének adott hangot, hogy a 3D tranzisztorok nem megfelelőek akkor, amikor igazán alacsony fogyasztás a cél, mivel ezeknél nem alkalmazható a dinamikus "body bias", amellyel felére csökkenthető a szivárgás üresjáratban. Dong Kyun Sohn, a Samsung Microelectronics kutatás-fejlesztési részegének vezetője elmondta, a koreai chipgyártó jelenleg tanulmányozza a 3D tranzisztorokban rejlő lehetőségeket, de lehet, hogy végül a "hagyományos", planáris megoldás továbbfejlesztése mellett dönt.

A hazai IT felrázásához haza kell hozni a legjobbjainkat Az elvándorolt szakemberek visszacsábítása komoly kihívás, azonban számos ország már megmutatta, hogy ez nem lehetetlen feladat.

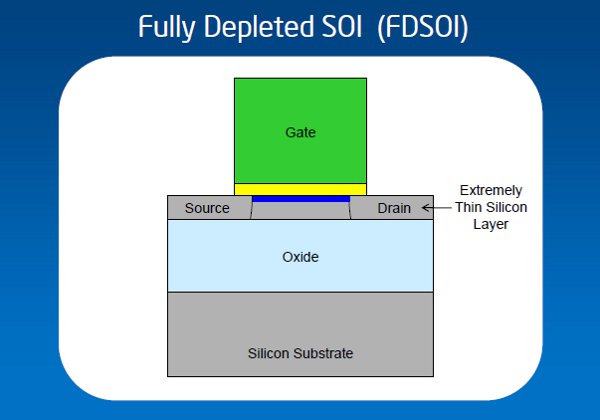

A planáris tranzisztorok előtt álló legvalószínűbb út az ún. fully depleted SOI (FD SOI) eljárás, amikor egy rendkívül vékony szilíciumfilm választja el a szigetelőréteget és a csatornát, csökkentve a szivárgást és növelve a kapcsolási sebességet. Az FD SOI megközelítés előnye, hogy a tranzisztorok nem térnek el jelentősen a ma használtaktól, ugyanakkor a gyártáshoz speciális FD SOI szilíciumszeletekre van szükség, amelyek drágák és nehezen beszerezhetők .

Az Intel is azért vetette el az FD SOI technológia használatát, mert a speciális waferek alkalmazása túlságosan megdrágítaná a gyártást - az Intel 10 százalékos költségnövekedésről beszél FD SOI waferek esetén, míg a háromkapus tranzisztorok bevezetésével mindössze 2-3 százalékkal drágul a gyártás a planáris tranzisztorokhoz képest. FD SOI waferekből ráadásul a kínálat is korlátozott, lehet hogy az Intel igényeit nem is tudnák kielégíteni a wafergyártók. "FD SOI waferekhez jutni nem egyszerű" - mondta Mark Bohr. "Ráadásul jelentősen meg is növelik a gyártás költséget, ezért az Intel nem használja ezeket."

22 nanométeres roham

Az Intel már elkötelezte magát a 3D tranzisztorok mellett és az év második felében megkezdi a 22 nanométeres csíkszélességgel gyártott Ivy Bridge kódnevű processzorok szállítását, hogy azok 2012 elejére a piacon lehessenek. Az Ivy Bridge az idén bemutatott Sandy Bridge mikroarchitektúra 22 nanométeres technológiára optimalizált verziója - a mai sajtóeseményen az Intel demózott is egy Ivy Bridge-alapú szervert, egy desktopot és egy notebookot, ezzel is mutatva, hogy mind a gyártástechnológia, mind a design készen van. Dadi Perlmutter elmondása szerint a 22 nanométeres Atom chipek az Ivv Bridge-nél később érkeznek, a HWSW tippje szerint 2012 második felében.

Egy tavaly őszi bejelentés szerint a világ legnagyobb chipgyártója 2011-ben és 2012-ben mintegy 6-8 milliárd dollár közötti összeget kíván üzemeinek modernizációjára fordítani, valamint egy új kutatás-fejlesztési célokat szolgáló gyár megépítésére. Az Intel új gyártástechnológia bevezetésekor előbb az oregoni D1D jelölésű referenciaüzemben dolgozza és érleli ki a megfelelő eljárásokat a rendkívül költséges berendezések és igen magas precizitást és szervezettséget megkövetelő folyamatok működtetéséhez, majd ezt a módszert mintegy hat hónapos tanulást követően más üzemekbe is átülteti. A D1D mellett a szomszédos D1C is részt vesz az elsőként 2009-ben demonstrált 22 nanométeres gyártástechnológia felfuttatásában, majd az Intel az arizonai Chandlerben lévő két gyárában és az izraeli Fab 28-ban is bevezeti az új eljárást.

A 22 nanométeres chipek előállításához továbbra is 193 nanométeres hullámhosszúságú, immerziós litográfiai berendezéseket alkalmaz a vállalat, így azokat még további évekig nem kell lecserélnie, ezzel több milliárd dollárt takarít meg. Az Intel mindent megtesz, hogy kihúzza az extrém ultraibolya fényt (13,5 nanométeres hullámhossz) használó eszközök életképessé válásáig, melyek korábban elérhetetlen felbontást tesznek lehetővé - cserébe rendkívül drágák és a nagy tisztaságú levegő helyett már vákuumot követelnek meg a működéshez, ami az üzemek átépítését is megkövetelheti, ami újabb költségekkel jár.