A jövő processzorába enged bepillantást az Intel kísérleti patkánya

A tavaly őszi Intel Developer Forumon már részletesen tárgyalta 80-magos, teraflops teljesítményű (ezer milliárd matematikai művelet másodpercenként) lapkáját a chipgyártó óriás. A chiptervezők éves dzsemborija, az ISSCC alkalmával újra elővették a prototípusokat, mivel az Intel mérnökei számos részletet osztanak majd meg azokkal kapcsolatosan a konferencián. A chip kísérleti terepként szolgál a jövőben olyan technológiák számára, melyek alkalmazása már szükségesnek tűnik a következő évtizedben, a teljesítmény fokozása érdekében.

Kísérleti patkány

Kísérleti patkány

Az Intel amerikai és indiai tervezőközpontjából érkező mérnökök egy olyan chipet mutatnak ma be az ISSCC-n (International Solid State Circuit Conference), mely 8 x 10-es elrendezésben homogén processzormagok hálózatát integrálja.

A 65 nanométeren implementált, Polaris névre hallgató lapka 100 millió tranzisztorból épül fel, 4 gigahertzes órajelen 98 wattot fogyaszt és 1 teraflops teljesítményt képes leadni, de akár 5,1 gigahertz elérésére is képes, 175 wattos fogyasztás mellett. Ezek a sarokszámok a masszívan párhuzamos felépítés energiahatékonyságbeli előnyét mutatják, hiszen a teraflopsos tartomány hússzorosan haladja meg a jelenleg elérhető legnagyobb teljesítményű processzorok teljesítményét.

A 80 kisméretű, egyszerűsített magból felépülő chip jelenlegi formájában kevéssé piacképes, vagy alkalmas valódi számítási feladatok hatékony futtatására, célja azonban nem is ez, hanem a kísérletezés, a sokmagos koncepció megvalósításához szükséges elektronikai és architekturális megoldások kidolgozása és kipróbálása.

Előbbiekhez tartozik a órajel-disztribúció és az energiagazdálkodás problematikája, vagyis hogyan érjük el a rengeteg mag megbízható működését agresszív órajeleken, méghozzá energiahatékony módon, miközben az energiatakarékosság jegyében az adott pillanatban nem, vagy kevéssé kihasznált magokon hogyan lehet azok lekapcsolásával, vagy működési feszültségük és órajelük csökkentésével wattokat megspórolni.

Processzorhálózat a chipen

Processzorhálózat a chipen

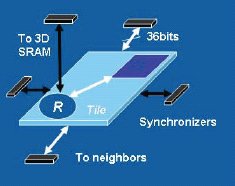

Architekturális oldalról két kulcskérdés merül fel: hogyan oldjuk meg a rengeteg mag közötti adatkommunikációt és vezérlést, továbbá hogyan etessünk egy teraflopsos teljesítményű processzort elegendő mennyiségű adattal?

Ilyen komplexitású felépítés és teljesítmény mellett az eddig kidolgozott kommunikációs megoldások elégtelennek bizonyulnak, így az IBM-Sony-Toshiba által kifejlesztett Cell 9 magját összekötő körbusz is, mely 3,2 gigahertzen 204,8 gigabájt másodpercenkénti sávszélességet biztosít.

A bemutatásra kerülő lapka egy kétdimenziós rácshálózatot alkalmaz, ahol a rácspontokat a magok képezik. Minden processzormagban egy hatportos router található, mely a beérkező adatcsomagról eldönti, hogy a beérkező adatcsomagot merre továbbítsa: a hozzá tartozó mag, valamelyik szomszédja, vagy pedig a memória felé. Egy ilyen router 80 gigabájt feldolgozására képes másodpercenként, késleltetése pedig 1,25 körül nanoszekundum körül alakul -- vagyis a chip egészén akár több terabájt aggregát sávszélesség is elérhető.

Szendvics

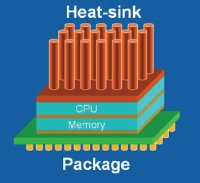

Hogy egy ilyen chipet hogyan látunk el megfelelő mennyiségű adattal, egy újabb jelentős problematika. A számítástechnika fejlődése során a memória egyre távolabb került a processzortól, vagyis sebessége nem tudott lépést tartani az órajelek és a számítási teljesítmény emelkedésével. Ezt a processzortervezők különféle technikákkal igyekeznek orvosolni, köztük az egyre duzzadó gyorsítótárakkal, és egyre okosabb előtöltési algoritmusokat alkalmazó logikával.

Egy 80-magos chip esetében azonban itt is áttörésre van szükség. Az Intel mérnökei szerint egy újabb szintre lesz szükség a memória hierarchiában, mégpedig a processzorhoz közel hozott DRAM-ra.

Egy 80-magos chip esetében azonban itt is áttörésre van szükség. Az Intel mérnökei szerint egy újabb szintre lesz szükség a memória hierarchiában, mégpedig a processzorhoz közel hozott DRAM-ra.

Az elképzelések szerint egy diszkrét DRAM-chipet illesztenének közvetlenül a processzorlapka aljára, így a fizikai közelség miatt lehetővé válna a chipek közötti alacsony késleltetésű, magas sávszélességű és energiahatékony kommunikáció. A processzorhoz rétegelt (stacked) DRAM-chip kapacitása viszonylag alacsony lenne, míg a nagyméretű, rugalmasan konfigurálható, ugyanakkor lassabb központi memória továbbra is megmaradna.

Heterogén felépítés?

A 80 homogén mag nem tekinthető iránymutatónak, ugyanis ez nem volt szempont a kísérleti design megalkotásakor. A következő évtizedben megjelenő sokmagos chipek, melyek gyártását a szakadatlan miniatürizáció teszi lehetővé, valószínűleg egyre inkább heterogén felépítésűek lesznek, bár ezzel kapcsolatban még nincs letisztult jövőkép iparban -- egyesek szerint a különféle utasításkészlettel bíró magok programozása túlságosan bonyolult és költséges.

A chipeket tervező mérnökök számára a tranzisztorbüdzsé kétévente közel megduplázódik (a jövő évtized elejére ötször, a közepére tizenötször annyi tranzisztort lesznek képesek a gyártók integrálni egy adott területre), miközben az energiabüdzsé nem lazul, sőt inkább egyre szorosabbá válik, főleg a hőfejlődés koncentrációjából fakadó thermodinamikai és elektronikai problémák miatt.

Ez azt jelenti, hogy az egy időben aktív tranzisztorok arányának egyre csökkennie kell, vagyis az integrációtól elmaradó ütemben növekszik a maximálisan megengedhető tranzisztoraktivitás. Hogy a teljesítmény emelkedésének üteme mégis megmaradjon, az áramkörök hatékonyságán kell javítani, ami alkalmazás-specifikus áramkörök implementációját vetíti előre: grafika, animáció, video, audio, fizika, mesterséges intelligencia, Javascript, Java, titkosítás, stb. terén.

A fejlődés irányát jelentősen befolyásolhatja a szoftveripar nagy része is, mely a chipgyártók mögött kullog, és még csak most ismerkedik a párhuzamosság paradigmájával. A chiptervezők feladata, hogy megtalálják az egyensúlyt a masszívan párhuzamos felépítés jelentette hatékonyság, valamint a programozási szempontból kedvezőbb erőteljes lineáris teljesítmény (erősebb magok) között.