Kezdődik a 22 nanométeres Intel rendszerchipek gyártása

A héten San Franciscóban zajló International Electron Devices Meeting (IEDM) konferencián mutatta be alacsony fogyasztású rendszerchipek gyártására optimalizált félvezetőtechnológiájának részleteit az Intel. Mark Bohr gyártástechnológiáért felelős vezető szerint jövőre elképesztő mobil chipek várhatók a cégtől.

Az Intel az év közepén dobta piacra első 22 nanométeres csíkszélességgel gyártott processzorait, az Ivy Bridge generációs Core család tagjait, mostanra pedig elkészült a gyártástechnológia módosított, kifejezetten alacsony fogyasztású rendszerchipekre (system on a chip, SoC) optimalizált változatával. Jövőre jöhetnek az első 22 nanométeres mobil chipek a cégtől, amelyek a 28 nanométeres versenytársakkal mérkőznek majd. "Egészen megdöbbentő SoC-kat fogtok látni 22 nanométeres technológián jövőre" - mondta Bohr.

SoC-gyártás háromkapus tranzisztorokkal

Az Intel 22 nanométeres technológiájának egyik legfontosabb jellemzője a 3D, másképp FinFET, az vállalat terminológiájában pedig Tri-Gate névvel illetett tranzisztor. A háromkapus tranzisztor alkotóelemei nem rétegszerűen helyezkednek el mint ahogy az korábban bevett volt, hanem háromdimenziós struktúrát alkotnak. A forrás (source) és a nyelő (drain) a szubsztrátból kiemelkedő vezetéken kap helyet, amelyet három oldalán érintve (tri-gate) satuszerűen fog közre a kapuelektróda (gate). A vállalat szerint a háromkapus felépítés lehetővé teszi, hogy a lehető legtöbb áram folyjon át a csatornán amikor a tranzisztor bekapcsolt állapotban van, és a legkevesebb, amikor ki van kapcsolva, illetve hogy a leggyorsabb legyen az átmenet a ki- és bekapcsolt állapotok között.

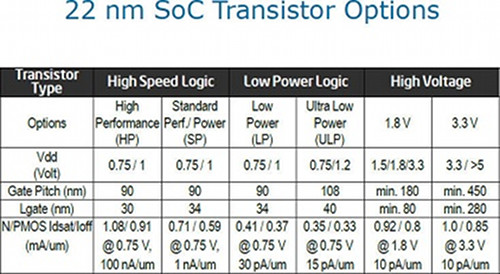

A rendszerchipek, gyártásához használt félvezetőgyártási eljárások fejlesztésével kapcsolatos legfontosabb kihívás, hogy a lapkákon vannak nagy teljesítményű, alacsony fogyasztású, ultraalacsony fogyasztású alkatrészek, amelyek eltérő karakterisztikájú tranzisztorokat igényelnek - emellett szükség van nagy feszültségű tranzisztorokra is, amelyekből a perifériákhoz közvetlenül kapcsolódó áramköröket lehet létrehozni. A sokféle eltérő és néha ellentétes igény miatt a gyártástechnológia finomhangolása időbe telik, a chipgyártó azonban váltig állítja, megtalálta a megfelelő receptet és 2013 elején beindul a 22 nanométeres rendszerchipek tömeggyártása.

Megélhetési IT: krónikus tünet vagy új normalitás? Amikor a szerelem, a hivatás megélhetéssé szelídül, a billentyűzet pedig szerszám lesz.

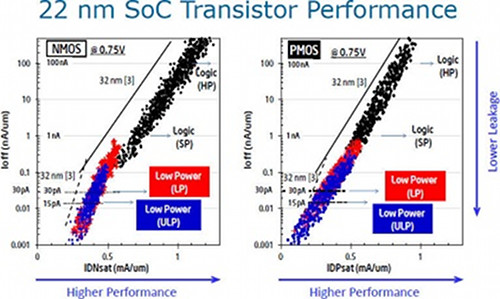

Mark Bohr előadása során kitért rá, hogy a szakmában egyöntetű kétkedés fogadta az Intel azon erőfeszítését, hogy a háromkapus tranzisztorokat sikeresen alkalmazza a rendszerchipekre optimalizált technológiáján. "Nos, ők láthatóan tévedtek" - szögezte le a gyártástechnológiai fejlesztésekért felelős vezető. Az SoC-gyártáshoz optimalizált 22 nanométeres eljárás tranzisztorai a 32 nanométeres planáris megfelelőikhez képest 20-65 százalékkal jobb teljesítménymutatókkal rendelkeznek, miközben szivárgási karakterisztikájuk is jobb azokénál. Bohr szerint a versenytársak 28 és küszöbön álló 20 nanométeres eljárásaihoz képest is előnyben van az Intel.

A kihívások

A másik probléma az alacsony fogyasztású eszközöknél a szivárgási áram, amely az alacsony fogyasztásra optimalizált chipeknél kiemelt fontosságú. A szivárgás a félvezetők lezárt átmenetén létrejövő jelenség, amely szabad elektronok és lyukak kombinációjából származik, a tápfeszültséggel fordítottan arányos és egy kisebb csíkszélességű gyártástechnológia bevezetésénél többszörösére is nőhet. "Ha szivárgásról van szó, a 30 pikoamperes nagyságrend elérése körül egyre több szivárgási forrással kell megbirkózni" - magyarázta Bohr. Szivárog a kapuoxid, szivárgás lép fel a forrás és a nyelő között, illetve a nyelő és a szubsztrát között is, ezeknek a kezeléséhez pedig a gyártástechnológiát kell némileg módosítani.

A nagy teljesítményű processzorok (pl. Ivy Bridge) és a rendszerchipek közti határok egyre inkább elmosódnak, mivel a processzorokra is egyre több funkció kerül rá, Bohr szerint azonban az SoC-k esetében az integráció mértéke szélsőséges rugalmasságot vár el a gyártástechnológiától. A most bemutatott P1271 kódnevű eljárás az Ivy Bridge generációs lapkák előállításához használt P1270 egyfajta kiterjesztéseként is felfogható, mondta el Mark Bohr. Ennek köszönhetően a két technológia ugyanabban a gyárban alkalmazható, az Ivy Bridge előállítása kapcsán eddig megszerzett tapasztalatok hasznosíthatók a kihozatal növelésére. A 22 nanométeres SoC-gyártási eljárás fejlesztéseit pedig 14 nanométeren is lehet hasznosítani, tette hozzá Bohr.

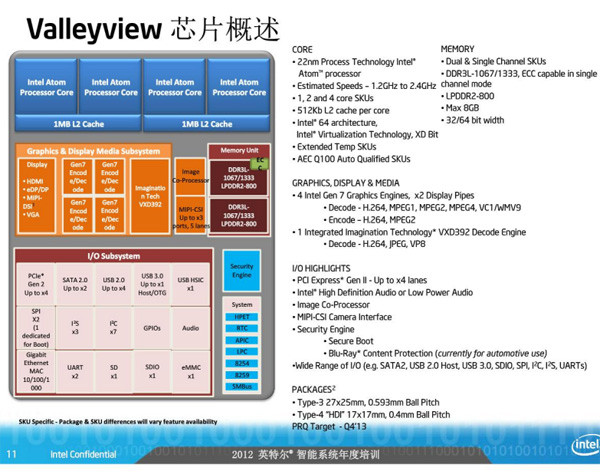

Valleyview

Korábban kiszivárgott információk szerint az első 22 nanométeres Atom rendszerchip a Valleyview kódnevet viseli. A lapkán kiviteltől függően 1, 2 vagy 4 darab 64 bites Atom processzormag kap helyet, amelyek vadonatúj, out of order mikroarchitektúrára épülnek, magonként 512 kilobájt L2 cache-sel gazdálkodnak, támogatják a Hyper-Threading technológiát és hardveres virtualizációs gyorsítással rendelkeznek. A várható órajel 1,2 és 2,4 GHz között van, feltehetően a több magos példányok órajele alacsonyabb, hogy a fogyasztás ésszerű keretek között maradjon. A Valleyview nagy dobása, hogy az Imagination Technologiestől licencelt GPU helyett az Intel Ivy Bridge-ben is található hetedik generációs Intel grafikus magot kapja meg, emellett többféle médiagyorsítóval is rendelkezik. A lapkán kiviteltől függően egy- vagy kétcsatornás memóriavezérlő kap helyet, valamint változatos IO interfészek (USB 3.0, SATA, SDIO).