A háromdimenziós processzoroké a jövő

[Real World Tech/HWSW] Tavaly decemberben az AMD hivatalosan is megkezdte első, 65 nanométeres csíkszélességgel gyártott chipjeinek forgalmazását. A Brisbane kódnevű lapka bár kisebb volt, és kevesebbet fogyasztott elődeinél, órajele elmaradt, és a mai napig elmarad a 90 nanométeres csúcsváltozatokétól, pedig papíron itt is tovább kellett volna lépnie. De mi is történt?

Moore ellenségei

A HWSW rendszeres olvasói számára ma már bizonyára elcsépelt közhely, hogy a processzorok és más logikai chipek teljesítményének növekedése mögött leginkább a Moore törvényeként ismert jelenség húzódik meg, amely szerint az adott szilíciumlapkára integrálható tranzisztorok száma nagyjából kétévente megduplázódik -- miközben a tranzisztorok gyorsulnak és kevesebbet fogyasztanak. Az immár több mint négy évtizede munkálkodó erő az utóbbi évtized során több problémába ütközött, melyek a miniatürizáció és a teljesítmény fokozása ellen dolgoznak.

Ennek egyik megnyilvánulása a már sokat tárgyalt szivárgási áram felerősödése, vagyis amikor az elektronfolyam, töltés áramlik oda, ahova nem kellene. Néhány ezer vagy száz atomnyi vastagságú anyagon ugyanis már átszivárognak az elektronok, a szigetelés elégtelenné válik. Ez a pazarlás egy modern processzor fogyasztásának negyedét is kiteheti, és ellensúlyozhatja a kisebb tranzisztorok kapcsolási fogyasztásának csökkenését.

A félvezetőgyártók ezt többek között új anyagok alkalmazásával próbálják orvosolni, továbbá alacsony szivárgású, lassabb áramköröket építenek a chip azon részein, melyek nem igénylik az alacsony késleltetést, vagyis az agresszív sebességet. Ilyen technikákkal vált lehetővé például, hogy a hatalmas L3 cache-t alkalmazó kétmagos Montecito (Itanium 2) kevesebbet fogyaszt, mint elődje, a Madison. Egy másik következménye az egyre kisebb struktúráknak, hogy érzékenyebbekké válnak a kozmikus háttér- és egyéb mikrohullámú sugárzással szemben, ami a bithibák exponenciális növekedésével jár -- de erről máskor.

A szakadatlan miniatürizáció egy másik ellensége nem a szilíciumlapkán keresendő, hanem az egyes funkcionális blokkokat összekapcsoló átkötéseknél (interconnect, azaz összeköttetés). A tranzisztorokkal ellentétben a fém összeköttetések teljesítménye a miniatürizációval, vagyis a méretek lefaragásával nem javul, hanem drasztikusan lecsökken, aminek okát minden elemi fizikaoktatáson átesett embernek ismernie kell: a vezető anyag vékonyodásával növekszik az ellenállása. Az ellenállás növekedésével pedig, ha emberi léptékben elhanyagolható mértékben, de növekszik a késleltetés is, bőven ellensúlyozva a kapacitás csökkenését.

A szakadatlan miniatürizáció egy másik ellensége nem a szilíciumlapkán keresendő, hanem az egyes funkcionális blokkokat összekapcsoló átkötéseknél (interconnect, azaz összeköttetés). A tranzisztorokkal ellentétben a fém összeköttetések teljesítménye a miniatürizációval, vagyis a méretek lefaragásával nem javul, hanem drasztikusan lecsökken, aminek okát minden elemi fizikaoktatáson átesett embernek ismernie kell: a vezető anyag vékonyodásával növekszik az ellenállása. Az ellenállás növekedésével pedig, ha emberi léptékben elhanyagolható mértékben, de növekszik a késleltetés is, bőven ellensúlyozva a kapacitás csökkenését.

A chip egymáshoz közel lévő blokkjai közötti összeköttetések esetében a vezetékek hosszának csökkenése ellensúlyozza ezt a kedvezőtlen trendet, ugyanakkor a tranzisztorok szempontjából relatíve így is csökken a sebesség. Tekintve, hogy a miniatürizációval a tipikus szilíciumlapkák mérete nem csökkent eddig, ennél sokkal súlyosabb problémát okoz a lapka távoli blokkjait összekötő, ún. globális összeköttetések teljesítményének folyamatos abszolút és relatív romlása. Az agresszív órajeleket megcélzó processzorok -- mint a Pentium 4 -- már teljes futószalag-fokozatokat dedikálnak a jel továbbítására, vagyis kényszerűségből pocsékolják el az órajelet, és a felvett energiát.

Probléma a gyakorlatban

Az AMD 65 nanométeres chipjeinek órajele az alacsonyabb fogyasztással lazuló energiakorlát és a gyorsabb tranzisztorok ellenére sem haladta meg vagy érte el a 90 nanométeres modellekét, amit lényegében a fentebb tárgyalt problémák, és az AMD félvezető-fejlesztési politikája magyarázhat. Mint az ismert, az AMD negyedéves ciklusban fejleszti gyártástechnológiáját, aminek segítségével folyamatosan javuló teljesítményt képes kicsikarni chipjeiből. Az első 90 nanométeres K8 chipek egy maggal 2,2 gigahertzen ketyegtek, ma két magból akár 3 gigahertzes órajelet is képes kipréselni a cég. A 65 nanométeres eljárás szempontjából tehát az AMD 90 nanométeres technológiája túlságosan magasra tette a lécet, és a 65 nanométeres változatok órajelét a összeköttetések késleltetése foghatja meg.

Az átkötések rendszere ráadásul a fogyasztási keret egyre nagyobb részét is maguknak követeli, akár többet mint amennyit valós számításokra fordít a chip, így a szivárgási árammal együtt nyugodtan kijelenthetjük, hogy a chipek energiafogyasztásuk töredékét fordítják valós számítások elvégzésére. A gyártók a trendet eddig jobb vezetőkre való áttéréssel (mint amelyen az alumínium rézzel való leváltása volt az ezredforduló derekán), valamint újabb és újabb, vastagabb, így gyorsabb összeköttetéseknek otthont adó réteg hozzáadásával kezelték. A tömegtermelésben és olcsón alkalmazható vezetők anyagok tárháza azonban véges, és a rétegek számának fokozása pedig nemcsak elégtelen válasz, de a gyártást is drágítja, nem beszélve a növekvő selejthányadról.

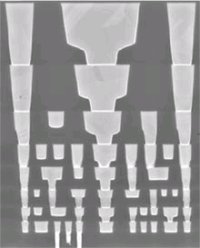

Felvétel réz összeköttetésekről

Mi akkor a megoldás? A valódi válasz a kérdésre ugyanaz lehet a közeljövőben, mint más esetekben is, mikor a jelterjedés késleltetése korlátozza a teljesítményt, például a memória vagy a perifériák elérése esetén: hozzuk közelebb egymáshoz a dolgokat. Ilyen lépés a memória- vagy PCI Express vezérlő chipre integrálása is, ezek azonban a jövőben elégtelennek bizonyulnak a processzorok teljesítményének további fokozódásával. Az Intel, és úgy tűnik, az iparág nagy része a jövőt a háromdimenziós felépítésben látja.

Eddig azonban többnyire komplett összetevők, mint a processzor és a DRAM egymásra rétegzéséről (stacking) volt szó, az összeköttetések körüli gondok azonban ennél finomabb megközelítést vetítenek előre, azaz egy-egy korábban monolitikus, lapos chip épül fel több diszkrét szilícium lapkából, és az egyes lapkák vertikálisan kerülnek integrálásra, szilíciumközötti összeköttetések révén.

Pentium 4 3D-Edition

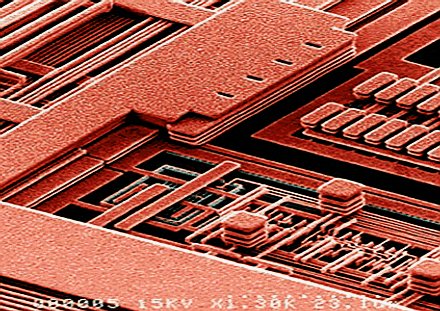

A Real World Techen megjelent egy cikk egy magát megnevezni nem kívánó szakértő tollából, melynek tanúsága szerint az Intel már kísérletezett egy Prescott-alapú Pentium 4 áttervezésével. A tavaly decemberben megrendezett 39. International Symposium on Microarchitecture konferencián az Intel mérnökei prezentálták az elért eredményeket. A vállalat nem végzett félmunkát, az optimalizálás során teljes funkcionális blokkokat darabolt fel és helyezett külön lapkára egymáshoz közel, amivel még a blokkon belüli késleltetés és a fogyasztás is redukálható.

Az 1 megabájtos másodszintű gyorsítótár kettéválasztásával a hozzáférés késleltetése 25 százalékkal, a hőleadás 20 százalékkal csökkent. A korábban rendkívül feszített időzítéseket alkalmazó utasításütemező háromdimenziós áttervezésével 15 százalékkal sikerült csökkenteni az összeköttetések késleltetését, ami a blokk áramköri felépítésének lazítását tette lehetővé: az újraoptimalizált és implementált blokk fogyasztása felére csökkent. Egyes funkcionális egységek közvetlenül az L1 cache-sel szemben, de a másik lapkán kaptak helyet. Összességében a 3D-s Pentium 4 futószalag-fokozatainak számát negyedével lehetett csökkenteni, enek köszönhetően a teljesítmény 15 százalékkal nőtt meg, mivel a téves elágazásbecslések kevesebb kieséssel jártak, és ugyanezek okból 15 százalékkal csökkent a fogyasztás.

A 3D-s Prescott-derivatíva tehát több mint 35 százalékkal energiahatékonyabbá vált egy újraimplementálás révén, vélhetően azonos órajelen mérve, adott teljesítményszintre normalizálva ez az előny már 60 százalék körülire ugrik, ami már szinte túl szép, hogy igaz legyen. A rétegzésnek azért van egy kiküszöbölhetetlen negatívuma, mégpedig a hődisszipáció problematikája. Mivel a rétegzett chipek disszipáló felülete lecsökkent, ráadásul melegítik egymást, így a maximális hőmérséklet a globális fogyasztás csökkenése ellenére is nőtt. Az azonos hőmérséklet elérése céljából csökkentett órajelen és feszültségen futó 3D-s chip teljesítménye ugyanakkor így is meghaladta a kétdimenziós designét.

Tömegtermelhetőségre várva

Tömegtermelhetőségre várva

Látható tehát, hogy a 3D-felépítésű chipek kecsegtetőek az összeköttetések jelentette növekvő problematika megoldására, ráadásul gyártási oldalról is előnyöket hozhatnak magukkal, hiszen az egyes, kombinálandó szilíciumszeletek mérete csökken, ami a selejtarány csökkenésével jár. Ehhez természetesen tömegtermelésben is bevethető 3D-integrációs eljárást kell kidolgozni, mely alacsonyabb hibaszázalékkal dolgozik.

Egy fejlett rétegzési technika ráadásul grafikus, DRAM és flash chipek egybetokozását is lehetővé teheti, ami nemcsak korábban nem látott kompaktságot, hanem energiahatékonyságot is magával hozna, remek jellemzőkkel a hordozható és ultraolcsó számítástechnika számára egyaránt. A flash-gyártók már megkezdték saját megoldásuk tökélyre fejlesztését, hogy egy adott szabványos tokba minél több memóriachipet tudjanak egymásra pakolni, mégpedig a szilícium szeletek vékonyítása révén. A Hynix a hónap elején közölte, hogy 20 NAND flash chipet sikerült egy iparágilag szabványos, 1,4 milliméter tokba helyeznie, melyek egyenként 25 mikrométer vastagok.

A témát részletesebben bemutató cikk elolvasható a Real World Tech magazin oldalán.