Kíméletlenül erős processzornak ígérkezik az Intel Nehalem

A HWSW rendszeres olvasói számára nem jelenthet újdonságot, hogy az Intel következő generációs architektúrája a Nehalem kódnevet viseli. A Nehalemről eleddig kevés információ látott napvilágot, megjelenésének közeledtével azonban természetesen elkezdte csöpögtetni a részleteket a vállalat.

Tovább csiszolt Core mikroarchitektúra

A Nehalemtől az Intel nem kevesebbet vár el, minthogy döntő és megkérdőjelezhetetlen teljesítményfölénybe kerüljön az AMD-vel szemben. Az eddig kiszivárgott (vagy szándékosan kiszivárogtatott) belső előrejelzések alapján a Nehalem látványosan nagyobb teljesítményt ad le, mint a jelenlegi CPU-generáció: a számításintenzív kódokat tartalmazó SPEC CPU2006 tesztek alatt, kétutas rendszerben 44 százalékkal múlja felül a jelenleg legerősebb négymagos Xeont egész számokkal végzett, és 104 százalékkal intenzív lebegőpontos műveletek alatt.

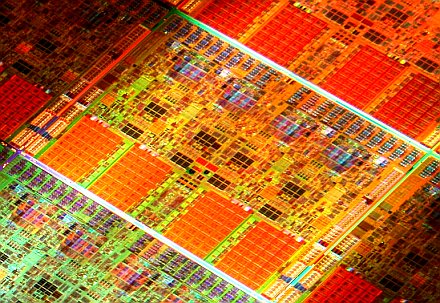

De miből áll össze ez a fölény? A következő generációs Intel-mikroarchitektúra első inkarnációjaként a 45 nanométeres eljáráson implementált, 731 millió tranzisztorból felépülő, 260 négyzetmilliméteres Nehalem négy nagyteljesítményű magot tartalmaz, melyek egyenként mintegy 25 százalékkal nagyobb területet emésztenek fel, ami már önmagában utal arra, hogy jóval erősebbek a Penrynénél. A processzor átszervezett cache-hierarchiával bír, a Nehalem 8 megabájt harmadszintű osztott tárral rendelkezik. Erőteljes változások azonban nem csak a chipet érintették, a Nehalem szakít ugyanis az Intel évtizedes buszrendszerével, és pont-pont összeköttetéseket, valamint integrált memóriavezérlőt vonultat fel.

A Nehalem a Merommal megismert Core mikroarchitektúra továbbfejlesztése. Hogy maximális teljesítményt préseljenek ki, az Intel tervezői erőteljesebb soronkívüli motorral vértezték fel a chipet. Az ütemező 96 helyett immár 128 mikroutasításból válogathat a végrehajtóegységek kihasználtságának fokozása érdekében -- vagyis emelkedhet az órajelenként elvégzett hasznos munka mennyisége. A Nehalem már SSE 4.2 vektor utaskészletet alkalmaz, mely további 7 alkalmazásspecifikus utasítást hoz magával elsősorban szövegek és stringek feldolgozásában, mint például az XML.

Szokás szerint továbbfejlődött az elágazásbecslés új, másodszintű becslők bevezetésével. Ezt a mérnökök a nagy kódtömegű alkalmazásokat (pl. adatbázisok) szem előtt tartva vetették be, melyek futtatása a többszintű becslés révén így hatékonyabbá válik, mondta el Ronak Singhal vezető tervező. A teljesítményt tovább javítja az egymástól független cache-hozzáférések gyorsabb végrehajtása, valamint a szinkronizációs primitívek gyorsítása, mely leginkább a többszálú végrehajtást támogatja. Egy másodszintű TLB (translation look aside buffer, memóriacím fordítási tár) bevezetésével gyorsulnak a virtuális-fizikai memóriacímek megfeleltetései, ami főként nagy memóriaigényű, memóriaműveletekben intenzív kódok alatt, így virtualizált környezetben jelenthet leginkább előnyt.

HyperThreading újratöltve

Változott a processzor cache-hierarchiája is, Singhal elmondása alapján egyértelműen háromszintű szervezésre tervezték és optimalizálták a Nehalemet. Ez főként abban mutatkozik meg, hogy a korábban osztott és nagyméretű L2 cache a Nehalem esetében magonként dedikált, és lényegesen kisebb méretű, 256 kilobájtos az alacsonyabb késleltetés elérése érdekében. Ahogyan az AMD Barcelona esetében, úgy az utolsó szintű L3 cache itt is az magok adatmegosztását és a processzorok közötti koherenciaforgalom kezelését hivatott támogatni. A Nehalem 8 megabájtnyi inkluzív, vagyis az L1 és L2 adatait is tartalmazó L3 tárral minimalizálja a koherencia miatti adatforgalmat, és egyelőre nem részletezett módon támogatja ezzel az energiagazdálkodást is.

A mikroarchitekturális fejlesztések leglényegesebbje azonban a többszálú végrehajtás ismételt bevetése. A 4-utasítás széles Core mikroarchitektúra szinte kínálta a többszálúságot, annak implementációja azonban valószínűleg kockázatkezelési okokból nem valósult meg a mielőbbi piacra kerülés érdekében -- a Core nagyjából fél évvel az eredetileg tervezett előtt került piacra, és többszálúság nélkül is visszavette a teljesítménytrónt.

A Nehalemben kétszálú párhuzamos végrehajtás (SMT, simultaneous multi-threading) kapott helyett, vagyis ebből a távolságból szemlélve olyan, mint amilyen a Northwood-magos Pentium 4-ben bukkant fel elsőként. Arra a kérdésre, hogy a Nehalem SMT-implementációja hogyan viszonyul a Pentium 4 Hyper-Threadinghez, Singhal úgy felelt, hogy a Nehalem sokkal több erőforrással, nagyobb gyorsítótárral és sávszélességgel bír, melyek mind-mind támogatják a többszálúságot. Singhal szerint 20-30 százalékos teljesítménynövekedés is elérhető megfelelően párhuzamosított szoftverek alkalmazása esetén, miközben minimális szilíciumba és energiába kerül a képesség megvalósítása -- vagyis ez bizonyult a teljesítménynövelés legenergiahatékonyabb módjának.

Gyökeresen új infrastruktúra

A mikroarchitekturális fejlesztések mellett a Nehalem lényeges változást hoz magával a rendszerinfrastruktúra terén is. Az új processzorcsaláddal, melynek a szerverektől kezdve egészen a notebookokig minden szegmensben felbukkannak a tagjai, az Intel megkezdi az évtizedek óta alkalmazott buszrendszer kivonását, és helyébe egy sokkal korszerűbb, pont-pont összeköttetésekre, és integrált memóriavezérlőre épülő architektúra lép.

A legelső Nehalem két Quick Path Interconnect linket (koherencia és távoli memória elérése, valamint I/O) és egy háromcsatornás DDR3-memóriavezérlőt alkalmaz, amelynek eredménye sokkal nagyobb sávszélesség egy nagyságrenddel alacsonyabb késleltetés mellett. Egy QPI-link akár 25,6 gigabájtos áteresztőképességre is képes (6,4 gigatranszfer másodpercenként egy 32 bit széles vonalon), miközben saját memóriáját 19,2 gigabájtos sávszélességgel éri el DDR3-800 memóriával.

Ez így akár 70 GB/s sávszélességet is biztosíthat egyetlen processzor számára szélsőséges esetben, míg egy 1600 megahertzes adatbusszal dolgozó Xeon 12,8 gigabájt/másodperccel gazdálkodik legfeljebb -- az Intel mérései szerint a valós memóriasávszélesség terén egy kétutas konfigurációban a Nehalem több mint négyszeres előnyre tesz szert. Mindezek után kevésbé meglepő, hogy az Intel legalább akkora előrelépést vár a Nehalemtől, mint amilyet a Core képviselt -- az kétségtelennek tűnik, hogy egy időre teljesen leszakítja magáról az AMD-t.

| SPECint_rate_base2006 | SPECfp_rate_base2006 | |

| Xeon Woodcrest | 178% | 278% |

| Xeon Clovertown | 79% | 161% |

| Xeon Harpertown | 44% | 104% |

| DC Opteron 3 GHz | 232% | 212% |

| Barcelona 2,3 GHz | 94% | 111% |

| Shanghai 2,8 GHz | 43% | 35% |

Lego design

Mint már említettük, a Nehalem mindössze az Intel következő generációjának első megtestesülése, később tucatnyi változatban lát majd napvilágot. Az egyes szegmenseket nagyban különböző designok szolgálják majd ki, ezért az Intel a mérnöki erőforrások optimalizálása érdekében kezdettő fogva moduláris blokkokként tervezte meg a Nehalemet, így lehetőség nyílik a blokkok (processzormag, cache, QPI link, grafikus mag, memóriavezérlő) tetszőleges kombinálásával különféle termékeket létrehozni.

Ezáltal lehetséges az, hogy az Intel úgy dobjon piacra nyolcmagos Xeon MP-ktől (Beckton) kezdve négymagos asztali processzorokon át kétmagos, integrált grafikus chippel bíró notebookprocesszort is a következő másfél év során, hogy ehhez nem szükséges aránytalanul sok fejlesztési erőforrást lekötnie. A egy- és kétutas szerverekbe, valamint felsőkategóriás asztali gépekbe szánt Nehalem a negyedik negyedévben jelenik meg a tervek szerint, majd az első negyedévben érkezik a mainstream négymagos asztali változat (Lynnfield), melyet a másodikban követ a belépőkategóriát célzó kétmagos Havendale és a mainstream mobil változat, az Auburndale -- utóbbi kettő érdekessége, hogy egy Direct X 10 grafikus magot, DDR3-vezérlőt és PCI Express vezérlőt integráló chipet tokoznak a kétmagos processzor mellé.