Hot Chips: bemutatkoztak az új SPARC processzorok

Palo Altóban véget ért a Hot Chips konferencia, a keddi napon pedig egyebek mellett bemutatkozott az Oracle és a Fujitsu következő generációs SPARC processzora is. Előző cég a SPARC M6-ot, utóbbi pedig a SPARC64 X+ lapka főbb paramétereit tette közzé.

Az Oracle idén tavasszal dobta piacra a SPARC T5 és M5 processzorait, amelyek közül előbbi a masszívan párhuzamos feladatokra optimalizált verzió 16 maggal, az M5 pedig inkább a magasabb szálszintű teljesítményt tartja szem előtt 6 magjával és hatalmas, 48 megabájtos harmadszintű gyorsítótárával. Mindkét processzor ugyanazokra az S3 magokra épül, amelyek legfeljebb 8 párhuzamos utasításszál futtatására alkalmasak.

M6: kétszer annyi mag

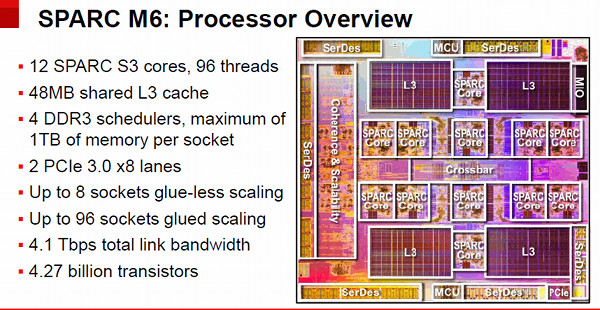

A tegnapi előadás szerint az M6 ugyanezekre az S3 magokra épül, azonban az M5-höz képest kétszer annyit, 12 darabot tartalmaz belőlük - ebben a tekintetben a chip a 16 magos T5 és a 6 magos M5 közé kerül a portfólióban, afféle kompromisszumot kínálva a nagy párhuzamosság és a nagy szálszintű teljesítmény között. Ami némileg meglepő, hogy a SPARC M6-ban a magszám duplázódását a megosztott L3 cache mérete nem követi, az továbbra is 48 megabájtos, vagyis az egy magra jutó L3 mérete 4 megabájt csupán. A processzor továbbra is 28 nanométeres csíkszélességű technológián készül, és majdnem 4,3 milliárd tranzisztort tartalmaz.

A chip "uncore" részének fontosabb jellemzői is az M5-öt idézik: maradt a négy darab DDR3 memóriavezérlő, a foglalatonként támogatott legfeljebb 1 terabájt operatív tár, a két darab integrált PCI Express 3.0 kontroller. A lapka a várakozások szerint kétszer akkora teljesítményt nyújt majd a kereskedelmi szerverfeladatok alatt, mint közvetlen elődje, az M5. Hogy ezt pontosan milyen alkalmazás vagy benchmark alatt kell érteni, azt nem tudni, és hogy mennyire valószerű becslés, annak eldöntéséhez túl kevés információt tudunk jelenleg, például az M6 órajele sem ismert paraméter most még.

Ha a méret a lényeg

A SPARC M6-nak két fontos tulajdonsága van: az egyik, hogy a processzor visszamenőlegesen foglalatkompatibilis az M5-tel, így az előző generációs gépeket megvásárló felhasználóknak biztosítja a továbblépést. Ez a lehetőség azonban valószínűleg keveseket érdekel majd, az M5-re alapozva ugyanis mindösszesen egy szervert mutatott be eddig az Oracle, a SPARC M5-32 modellt, amely 32 processzorral rendelkezik és high-end modellhez méltó árcímkét is kapott, következésképpen valószínűleg viszonylag keveset is adtak el belőle. A SPARC M5 és M6 egyébként egy gépben is működhet együtt, vagyis az ügyfelek akár fokozatosan is áttérhetnek a régebbi processzorról az újabbra.

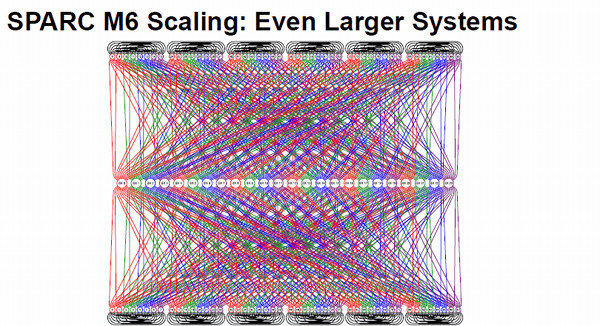

Egy 96 foglalatos M6 rendszer topológiája (ha sokáig nézi valaki, 3D-ben jelenik meg Larry Ellison)

Az új chip igazán nagy dobása a Bixby kódnevű alkalmazásspecifikus integrált áramkör. A SPARC M6 külön vezérlő nélkül 8 foglalatig képes skálázódni (hasonlóan a T5-höz), azonban a cache koherenciát biztosító Bixby lapka segítségével extrém méretű, 96 foglalatos osztottmemóriás rendszer építhető (Bixby egyébként egy város Oklahomában). Egy ilyen, 96 foglalatos szörnyeteg 1152 processzormaggal rendelkezik, amelyek egy időben legfeljebb 9216 programszálat tudnak párhuzamosan végrehajtani. A maximális memóriakapacitás a foglalatonkénti 1 terabájtos limitet figyelembe véve 96 terabájt lehet - egy esetleges SPARC M6-96 ideálisnak tűnik nagy adatintenzitású alkalmazások futtatására, legyen szó akár online tranzakciófeldolgozásról, akár "big data" jellegű feladatokról.

Egyelőre nem tudni, lesz-e 96 foglalatosnál kisebb SPARC M6-alapú gép, mint ahogy az M5-ből sem volt 32 foglalatosnál kisebb, de valószínűnek látszik, hogy lesz. A 32 processzoros rendszer gyakorlatilag készen van, elég hozzá a SPARC M5-32 gépben kicserélni a chipeket M5-ről M6-ra, és egy 48 processzoros rendszernek is lenne értelme. A Hot Chipsről származó helyszíni beszámolók szerint az Oracle előadója, Ali Vahidsafa vezető hardvertervező mérnök nem kívánt semmilyen részletet elárulni arról, milyen konfigurációkban lesz elérhető az M6, és arról sem mondott semmit, hogy mikor érkezik a piacra. Tekintve, hogy elődje, az M5 alig pár hónapos, nagyon nem sietős az Oracle dolga.

Fujitsu SPARC64 X+: HPC-re tervezve

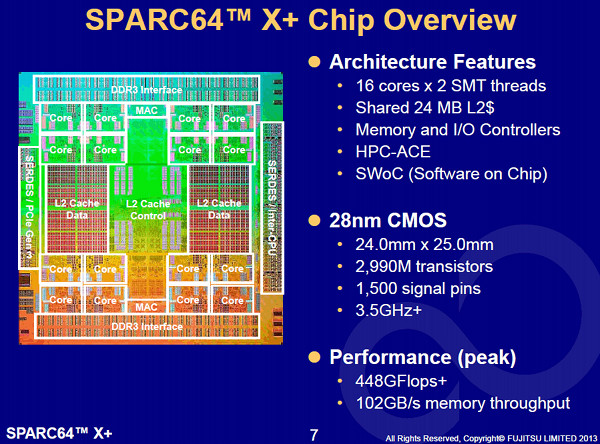

A nap másik SPARC chipje a Fujitsu következő generációs lapkája, a SPARC64 X+ volt. Amint a neve is mutatja, ez a chip csak kisebb előrelépést képvisel a SPARC64 X-hez képest (bár az igazat megvallva, a SPARC M6-ra is jobban illene talán a SPARC M5.5 modellszám). A SPARC64 X idén januárban debütált, ennek finomhangolásával jött meg a SPARC64 X+, amely az elhangzottak szerint három fontos területen lépett előre.

Az egyik fontos változás az órajel, feltehetően a design és a gyártástechnológia jobb összecsiszolásának köszönhetően a SPARC64 X+ 3,5 GHz-en fog nyitni és később ennél magasabb frekvenciát is elérhet - a SPARC64 X-ből 3 GHz-es a leggyorsabb verzió jelenleg. A vetített prezentáció szerint a chip továbbra is 16 magos, magonként 2 szálat kezel és még mindig 28 nanométeres csíkszélességgel készül. Maradtak a cache-méretek és a memória-sávszélesség sem változott.

Nyerd meg az 5 darab, 1000 eurós Craft konferenciajegy egyikét! A kétnapos, nemzetközi fejlesztői konferencia apropójából a HWSW kraftie nyereményjátékot indít.

A tranzisztorszám 2,99 milliárdról 2,995 milliárdra emelkedett, a különbséget feltehetően a HPC-ACE utasításkészet beépítése okozza. Ezt az utasításkészlet-kiterjesztést a kimondottan mérnöki-tudományos számítások elvégzésére tervezett, a világ egykor leggyorsabbjának számító K Computerben is alkalmazott Fujitsu SPARC64 VIIIfx processzorból ismerhetjük. A HPC-ACE az általános célú és lebegőpontos regiszterek számát is megnöveli (magonként 192+256-ra), tartalmaz 7 új lebegőpontos utasítást, és támogatja két SIMD utasítás párhuzamos végrehajtását, illetve 8 lebegőpontos utasítás egyidejű végrehajtását.

A harmadik változás a memóriakonfigurációt érinti. A SPARC64 X "csak" fél terabájtot támogat foglalatonként, a SPARC64 X+ azonban ezt 1 terabájtra növeli. A jelenlegi legnagyobb X-alapú gép 64 foglalatos, de csak 32 terabájtos, az X+ használatával ez duplájára nőhet. A helyszíni beszámolók szerint vannak még kisebb újítások a processzorban, a mérnökök finomhangolták az elágazásbecslőt, állítólag érkezik egy új "integer byte compare" utasítás is és növekszik a processzorok közti kommunikáció sebessége is.

A cég kitart a SPARC64 mellett

A SPARC64 X+ felvillantott specifikációi alapján a processzort mérnöki-tudományos területre szánja a Fujitsu, egyelőre nem tudni, vajon a kereskedelmi feladatokra szánt M10 sorozatú gépekbe bekerülnek-e. A válasz valószínűleg igen, de hogy mikor és milyen konfogurációban, arról egyelőre semmit sem tudni. Ami viszont biztos, hogy a Fujitsu a jövőben is folytatni fogja a SPARC64 család fejlesztéseit, az előadását legalábbis ezzel a kijelentéssel zárta Toshio Yoshida, a cég mérnöke.