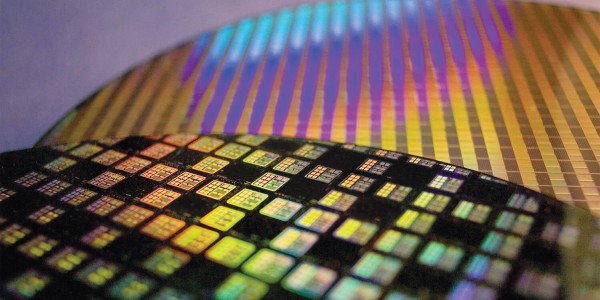

Óramű pontossággal fejleszt a TSMC

A tajvani cég friss bejelentései szerint sínen vannak a következő gyártástechnológiák.

Két pozitív hírrel szolgált kurrens fejlesztéseivel kapcsolatban a TSMC. A piacvezető bérgyártó elmondása alapján mind a második generációs 7 nanométer, mind pedig az azt követő 5 nanométer fejlesztése a tervek szerint halad. Előbbi állapotáról árulkodik, hogy a tajvani vállalat egyik meg nem nevezett partnerével (Apple?) közösen már elérte a tape-out fázisát, vagyis a chipdizájn terveit véglegesítették a mérnökök, és optimális esetben pár hónap múlva megkezdődhet a próbagyártás. Hasonlóan jól haladnak az 5 nanométer munkálatai, a tranzisztorsűrűségben lényegesen nagyobb előrelépéssel kecsegtető gyártástechnológia próbagyártását már jövő áprilisban beindítaná a TSMC.

A CLN7FF+ kódnevű második generációs 7 nanométer fejlesztése tehát a tervek szerint halad. A bérgyártó ettől körülbelül 20 százalékkal magasabb tranzisztorsűrűséget, illetve 6-12 százalékkal alacsonyabb fogyasztást ígér. Ennek egy részét a régóta halogatott EUV technológia biztosíthatja, amelyet ezzel elsőként vetne be élesben, vagyis tömegtermelésben a TSMC. Ahogy arról korábban már többször írtunk, az extrém ultraibolya fénnyel dolgozó technológia számos buktatót rejt, ezért a gyártók rendkívül óvatosan állnak a technológiához, illetve annak bevetéséhez. Ebből kifolyólag a bonyolult és költséges megoldást az első nekifutást jelentő CLN7FF+ esetében csak a gyártási folyamat egy kis részénél, pontosabban a nem kritikus rétegeknél veti be a tajvani bérgyártó, ily módon ugyanis kordában tarthatóak a költségek, illetve csökkenthető a meglehetősen magas rizikó.

Égbe révedő informatikusok: az Időkép-sztori Mi fán terem az előrejelzés, hogy milyen infrastruktúra dolgozik az Időkép alatt, mi várható a deep learning modellek térnyerésével?

A TSMC első "igazi" EUV-s eljárása az 5nm lesz. A CLN5FF kódnevű gyártástechnológánál a TSMC szélesebb körben veti be az egyelőre gyerekcipőben járó EUV-t, friss hírek szerint az egyes chipdizájnok már akár 14 rétegét is az extrém ultraibolya fénnyel rajzolhatják meg. Ennek hála jelentős mértékben nőhet a sűrűség, az EUV-t még nélkülöző CLN7FF-hez képest akár 80 százalékkal is több tranzisztor helyezhető majd el egységnyi szilíciumon, ami egységnyi tranzisztorszámmal kalkulálva 45 százalékkal kisebb területű chipeket jelenthet. Fogyasztás, illetve a tranzisztorteljesítmény tekintetében már jóval kisebb előrelépést hozhat az eljárás, előbbinél 20, utóbbinál pedig 15 százalékos lehet a javulás - de nem egyszerre. A valós érték attól függ majd, hogy a tervezésnél melyik tulajdonságot részesítik előnyben a mérnökök.

Egekbe szökő költségek

Ahogy a TSMC néhány hónapja bejelentette, az 5 nanométeres chipek termeléséhez egy dedikált gyárkomplexumot épít. A Fab 18-ra keresztelt üzem felállítása összesen nagyjából 17 milliárd dollárt emészt majd fel. Ebből többek között nagyjából 160 000 négyzetméternyi tisztaszobát húz fel a vállalat, a komplett gyárkomplexum pedig 950 000 négyzetméteren terül majd el. Előbbi közel 60, utóbbi pedig nagyjából 120 százalékkal haladja meg a hasonló kapacitásra képes Fab 15 paramétereit. A tetemes eltérés oka, hogy a modernebb gyártástechnológiához szükséges különféle eszközök (pl. EUV levilágító) a megszokottnál jellemzően sokkal nagyobb helyigénnyel rendelkeznek.

Jelen állás szerint a TSMC már jövő áprilisban megkezdené az 5 nanométeres chipek kísérleti gyártását, a tömegtermelés pedig a Fab 18 megnyitásával, 2020 második negyedévében indulhat meg. A tervezett maximális kapacitását 2021 második felében érheti el az üzem, amit körülbelül évi 1 millió megmunkált 300 milliméteres szilíciumostyában szabott meg a TSMC. Az egyre magasabb fejlesztési költségek természetesen a partnereknél csapódnak le. Az EETAsia információi szerint egyetlen 5 nanométeres chipdizájn (tehát egyetlen chiptípus) gyártásra való előkészítése 200-250 millió dollárra rúg majd, ami számottevőn több a 10 és 7 nanométeres fejlesztésekhez szükséges, nagyjából 150 millió dolláros összegnél. Ennek fényében várhatóan egyre kevesebb partner, egyre lassabban fog átállni az új csúcskategóriás gyártástechnológiákra.