Toshiba: 1 terabájt kapacitás egyetlen chipben

A vállalat NAND chipekben elsőként vetette be a TSV tokozási eljárást. Rekord nagy SSD-k jöhetnek.

Rekordkapacitású NAND chipet jelentett be a Toshiba. A fejlesztés 3D NAND lapkákat tartalmaz, amelyeket a gyártó elsőként párosított a TSV (through-silicon via) tokozási eljárással. A végeredmény egy nagy, legfeljebb 1 terabájt tárkapacitású, nagy sávszélességű, végül, de nem utolsó sorban pedig alacsony fogyasztású komponens, amellyel az eddigieknél lényegesen nagyobb SSD-k építhetőek.

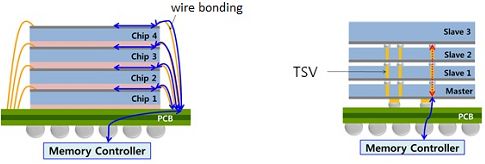

A TSV technológia nem számít újnak, ugyanakkor az eddig csak DRAM chipeknél alkalmazták, például a Samsung lassan két éve ezzel készítette el első 128 gigabájtos memóriamodulját. A technológia lényege, hogy a chipen belüli lapkák összekötésében és elrendezésében rejlik. Egyetlen tokozáson belül több lapkát is el lehet helyezni, amihez az úgynevezett wire-bonding a legnépszerűbb eljárás, ennél a vezetékek az egyes lapkák szélein futnak végig a chip alján található érintkezőkig.

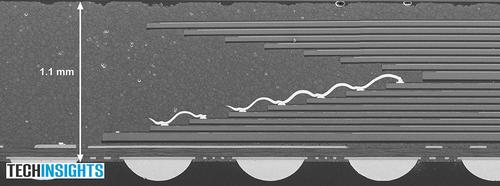

Wire-bonding a röntgen alatt

Ezzel szemben a TSV-nél az egymásra rétegezett szilíciumlapkákon keresztül (innen az elnevezés), pontosabban az azokon belül kialakított több száz járaton keresztül futnak végig a vezetékek. Ezzel elhagyható az egyes lapkák közötti relatíve vastag elválasztóréteg, ráadásul a huzalok hossza is jelentősen redukálható, így a kvázi sztenderd megoldáshoz viszonyítva több lapka helyezhető egymásra, tehát növelhető a kapacitás, eközben pedig a rövidebb vezetékeknek hála csökken a fogyasztás, és/vagy nő az átviteli sebesség. Az eljárás nem keverendő a különféle 3D NAND-os megoldásokkal, ahol egyetlen szilíciumlapkán belül építik ki a vertikális cellastruktúrát különféle levilágítási eljárások segítségével.

Bár a TSV számos előnnyel kecsegtet, a technológia alkalmazása korántsem triviális feladat (értsd: drágább), ahhoz ugyanis speciális lapkák szükségesek. A Toshibának ezért egy kifejezetten ehhez tervezett dizájn kellett kidolgoznia a megfelelő érintkezőpontokkal felszerelve. Ehhez a cég a korábbi, BiCS2 (TLC) fejlesztést vette alapul, amelyben az aktuális legújabb, BiCS3 64 rétegéhez képest "csak" 48 cellaréteg található. Ennek egyik oka vélhetően a könnyebb gyártásban rejlik, kevésbé komplex dizájnban egyszerűbb kialakítani a TSV-hez szükséges huzalozást.

Nyerd meg az 5 darab, 1000 eurós Craft konferenciajegy egyikét! A kétnapos, nemzetközi fejlesztői konferencia apropójából a HWSW kraftie nyereményjátékot indít.

A végeredmény egy 14 milliméter széles és 18 milliméter mély x8 BGA-152 felületű chip lett, amely 1,35 milliméteres magasság mellett 512 gigabájt, 1,85 milliméter mellett pedig 1024 gigabájt kapacitást kínál 1066 MT/s maximális sávszélesség mellett. Utóbbi kifejezetten jó érték, a konkurens Samsung közelmúltban bemutatott 64 rétegű lapkákra épülő fejlesztés "csak" 800 MT/s értékre képes.

A Toshiba már szállítja új fejlesztéseinek prototípusát, a gyártó első körben vállalati SSD-kbe szánja TSV-s NAND-ját. Ennek kézenfekvő oka, hogy az új chipek előállítása költséges, amelyet könnyebb a drága, adatközpontos termékekkel kitermelni, miközben a nagy kapacitású chipek előnye is könnyen kiaknázható a kapacitása és fogyasztásra egyaránt érzékeny környezetben. A chipekkel szerelt első piacképes termékek jövőre jelenthetnek meg.